AMD Previews EPYC ‘Rome’ Processor: Up to 64 Zen 2 Cores

by Anton Shilov on November 6, 2018 2:27 PM EST

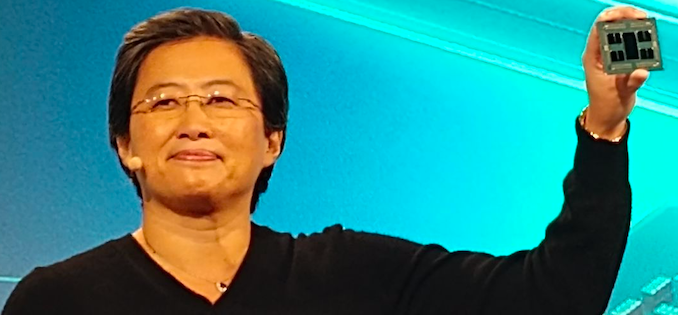

AMD on Tuesday formally announced its next-generation EPYC processor code-named Rome. The new server CPU will feature up to 64 cores featuring the Zen 2 microarchitecture, thus providing at least two times higher performance per socket than existing EPYC chips.

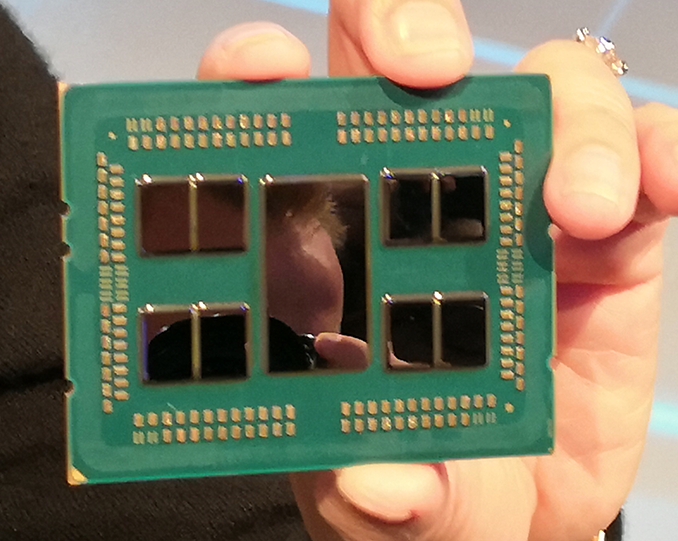

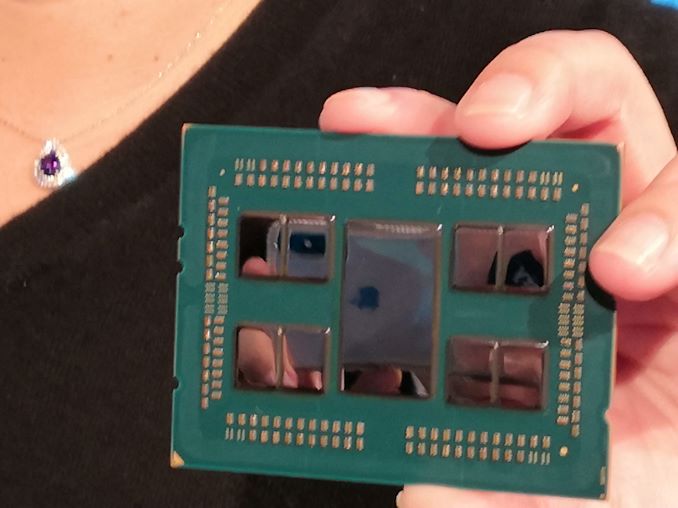

As discussed in a separate story covering AMD’s new ‘chiplet’ design approach, AMD EPYC ‘Rome’ processor will carry multiple CPU chiplets manufactured using TSMC’s 7 nm fabrication process as well as an I/O die produced at a 14 nm node. As it appears, high-performance ‘Rome’ processors will use eight CPU chiplets offering 64 x86 cores in total, as well as an eight-channel DDR4 memory controller supporting up to 4 TB of DRAM per socket. Besides, the new processor supports 128 PCIe 4.0 lanes to connect next-generation accelerators, such as the Radeon Instinct MI60 based on the Vega 7nm GPU.

Considering the fact that Zen 2 microarchitecture is expected to generally increase performance of CPU cores (especially when it comes to floating point performance, which AMD expects to double), the Rome processors will boost performance of servers quite dramatically when compared to existing machines. In particular, AMD expects performance per socket to double as a result of higher core count, and predicts that floating point performance per socket will quadruple because of arhitectural IPC improvements and increase of the core count.

One important peculiarity of AMD’s EPYC ‘Rome’ processor is that it is socket compatible with existing EPYC ‘Naples’ platform and will be forward compatible with AMD’s future ‘Milan’ platforms featuring CPUs powered by the Zen 3 microarchitecture. This will greatly simplify development of AMD-based servers and will enable server makers to reuse their existing designs for future machines, which is important for AMD that needs to capture market from Intel. To do that, it has to simplify job of server builders by making its platforms simple.

AMD is currently sampling its EPYC ‘Rome’ processor with server makers and customers. The company plans to launch ‘Rome’ products sometimes in 2019, but it does not disclose its launch schedule just now.

This is a breaking news. We are updating the news story with more details.

67 Comments

View All Comments

Tuna-Fish - Tuesday, November 6, 2018 - link

The memory controllers and other IO take up the perimeter of the chip. An IO chip with 2 IF controllers for 2 core chiplets and 2 channels of DDR could be 1/16th of the size. (as size increases, perimeter goes up at a rate of 2x while area goes up at a rate of x^2)Of course, most of the area of that IO chip will actually be cache. It will be interesting if the Ryzen IO chip will have a L4 cache, and if it will, how large will it be.

cheshirster - Wednesday, November 7, 2018 - link

Cache is not planned on the IO chip.eva02langley - Tuesday, November 6, 2018 - link

If AMD can double the core counts on EPYC, they can do the same for their other range of CPU.Hul8 - Tuesday, November 6, 2018 - link

More than 8 cores doesn't make that much sense for mainstream that will still be limited to 2 channel memory and 24 PCIe lanes. AMD will like to sell you Threadripper instead if you want more cores.Where I can see the benefit is cramming one 8-core core (maybe 6 of those enabled) chiplet, a larg(ish) GPU chiplet, an I/O die - and maybe a stack of HBM - on a single package and making thin-and-light laptops with good enough performance for mainstream gaming. Separating CPU and GPU will allow AMD to create a lot more APU variants with essentially the same resources.

SaturnusDK - Tuesday, November 6, 2018 - link

It think it's more than likely they'll do 16 core for next gen R7s but without SMT, or with hybrid SMT where the two fastest cores are left without SMT and the two slowest is run with SMT for 16c/16t or 16c/24t.And then naturally a high graphics performance variant with a HBM2 chiplet, a Vega Mobile chiplet, one 8 core chiplet, and an IO controller.

Martin_Schou - Tuesday, November 6, 2018 - link

Well ... AMD could light a fire under Intel's behind if they wanted to. Take a slightly defective I/O die with only four RAM channels and 64 CPU PCIe 4.0 lanes, hook up four 4-core CCXs and Vega 20 GPU and call it their high-end desktop processor (below Threadripper). Limit the chipset to only handling 4 RAM slots to avoid eating into older Threadrippers too much, but sadly I suspect you're right.But it's fun to imagine. Then again, I suppose you could do something like this to make a high-end mobile CPU instead? Maybe you could get a MacBook with 6+ cores that doesn't end up melting itself?

Hul8 - Tuesday, November 6, 2018 - link

AMD doesn't have a socket with 4 memory channels, 64 PCIe lanes and video connectivity.The whole idea of AM4/TR4+chipsets divide is to cut costs; AM4 provides enough connectivity for most people and TR4 serves the rest.

The intersection of people interested in high performance but not discrete graphics is so small it really doesn't pay to create a special socket for just them. And motherboard vendors wouldn't adopt it anyway, because they couldn't expect good sales.

Hul8 - Tuesday, November 6, 2018 - link

It doesn't mean that such a CPU could never see the light of day, but it would be soldered onto thin-and-light laptops and maybe AIOs.Namisecond - Tuesday, November 6, 2018 - link

64 PCIe 4.0 lanes, Vega 20 GPU and 4 memory slots in a sealed thin and light laptop? Especially a mac?Sounds more like a proprietary workstation or server board.

abufrejoval - Wednesday, November 7, 2018 - link

I think they call them gaming consoles.