Update: PCI Express 6.0 Draft 0.71 Released, Final Release by End of Year

by Ryan Smith on July 2, 2021 7:00 AM EST- Posted in

- CPUs

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

Update 07/02: Albeit a couple of days later than expected, the PCI-SIG has announced this morning that the PCI Express draft 0.71 specification has been released for member review. Following a minimum 30 day review process, the group will be able to publish the draft 0.9 version of the specficiation, putting them on schedule to release the final version of the spec this year.

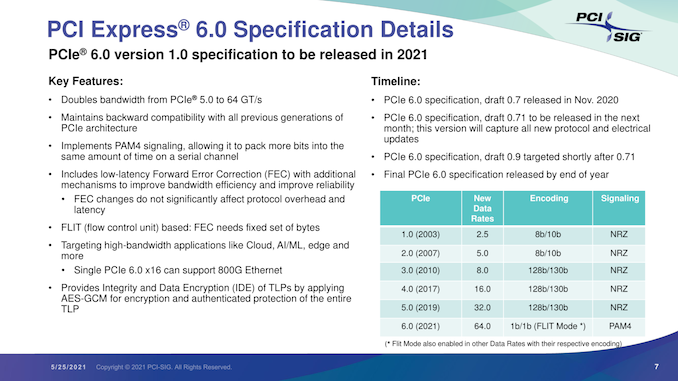

Originally Published 05/25

As part of their yearly developer conference, the PCI Special Interest Group (PCI-SIG) also held their annual press briefing today, offering an update on the state of the organization and its standards. The star of the show, of course, was PCI Express 6.0, the upcoming update to the bus standard that will once again double its data transfer rate. PCI-SIG has been working on PCIe 6.0 for a couple of years now, and in a brief update, confirmed that the group remains on track to release the final version of the specification by the end of this year.

The most recent draft version of the specification, 0.7, was released back in November. Since then, PCI-SIG has remained at work collecting feedback from its members, and is gearing up to release another draft update next month. That draft will incorporate the all of the new protocol and electrical updates that have been approved for the spec since 0.7.

In a bit of a departure from the usual workflow for the group, however, this upcoming draft will be 0.71, meaning that PCIe 6.0 will be remaining at draft 0.7x status for a little while longer. The substance of this decision being that the group is essentially going to hold for another round of review and testing before finally clearing the spec to move on to the next major draft. Overall, the group’s rules call for a 30-day review period for the 0.71 draft, after which the group will be able to release the final draft 0.9 specification.

Ultimately, all of this is to say that PCIe 6.0 remains on track for its previously-scheduled 2021 release. After draft 0.9 lands, there will be a further two-month review for any final issues (primarily legal), and, assuming the standard clears that check, PCI-SIG will be able to issue the final, 1.0 version of the PCIe 6.0 specification.

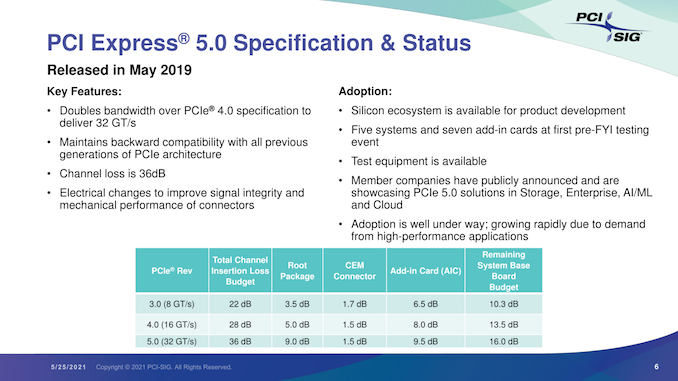

In the interim, the 0.9 specification is likely to be the most interesting from a technical perspective. Once the updated electrical and protocol specs are approved, the group will be able to give some clearer guidance on the signal integrity requirements for PCIe 6.0. All told we’re not expecting much different from 5.0 (in other words, only a slot or two on most consumer motherboards), but as each successive generation ratchets up the signaling rate, the signal integrity requirements have tightened.

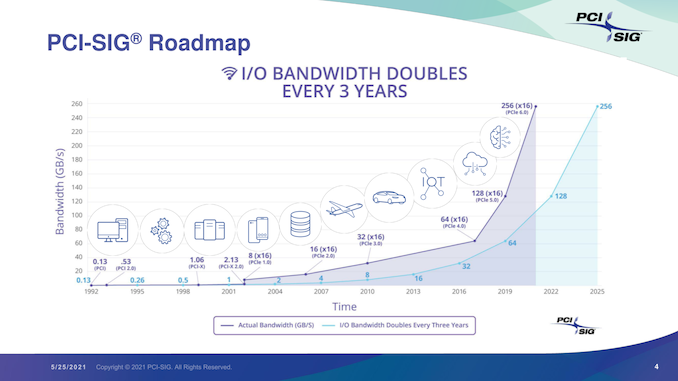

Overall, the unabashedly nerdy standards group is excited about the 6.0 standard, comparing it in significance to the big jump from PCIe 2.0 to PCIe 3.0. Besides proving that they’re once again able to double the bandwidth of the ubiquitous bus, it will mean that they’ve been able to keep to their goal of a three-year cadence. Meanwhile, as the PCIe 6.0 specification reaches completion, we should finally begin seeing the first PCIe 5.0 devices show up in the enterprise market.

103 Comments

View All Comments

CiccioB - Thursday, May 27, 2021 - link

Oh, I forgot the costs. It also depends on how much you want your transmission to be complex to build and so how much it will cost in term of pure $$$.mode_13h - Saturday, May 29, 2021 - link

This doesn't seem very useful. It would've been simpler and more accurate to say "I don't know", which is clearly the case. You probably never designed a PCB in your life.mode_13h - Wednesday, May 26, 2021 - link

Ryan Smith> All told we’re not expecting much different from 5.0Ryan Smith> (in other words, only a slot or two on most consumer motherboards)

And which consumer motherboards are you seeing this on, Ryan Smith?

Wereweeb - Wednesday, May 26, 2021 - link

Alder Lake is confirmed to use PCIe 5.0mode_13h - Thursday, May 27, 2021 - link

> Alder Lake is confirmed to use PCIe 5.0I know that, but it hasn't been disclosed where or how. I'm asking how the author seems to know that "most" of its consumer motherboards will have "only a slot or two").

To the extent of any evidence I've seen, Alder Lake could just use PCIe 5.0 for its DMI link. If Ryan Smith definitely knows otherwise, I'd like him to confirm.

CiccioB - Thursday, May 27, 2021 - link

Making a public announcement of supporting a technology and then bury it only for internal use (which is not interesting to any consumer) would not be a good move. IMHO.So AL will probably have an external link PCIe 5 (4 lanes?) from CPU towards what can be simply a single SSD slot, just to say: we can be faster than the competition, and at the first device supporting that technology they can beat on that nail for months.

The number of lanes will be few as they are very critical copper traces and cost a lot, so motherboards cannot be that expensive just for adding a technology that is not really beneficial today (and probably for the next 5 years but just for a small 0.x% amount of PC users).

I think that the balance will be having few lanes for imagine purpose but not too many for not going up with costs and energy consumption.

On laptop PCIe5 may be useful for limiting the lanes going towards the classic x4 connection towards the dGPU. GPU producer may spare some money and energy in supporting PCI5 with the added option to also advertising that feature just to give impression that the GPU will be even faster (you know, 3.0<4.0<5.0 and big numbers always matter! Give me a 200Mpixel sensor on that smartphone!).

mode_13h - Saturday, May 29, 2021 - link

> Making a public announcement of supporting a technology and then bury it only for> internal use (which is not interesting to any consumer) would not be a good move.

A lot of features and specs are just for bragging rights. Also, they could be trying to push AMD into a very expensive mistake.

Qasar - Friday, July 2, 2021 - link

how would this push amd to make a very expensive mistake ? couldnt it also push intel to do the same ?mode_13h - Sunday, July 4, 2021 - link

> how would this push amd to make a very expensive mistake ?If Intel is only adding PCIe 5.0 for the CPU-chipset link, all the noise they're making about it could scare AMD into adding it for all PCIe lanes, thinking that's what Intel is doing.

Qasar - Sunday, July 4, 2021 - link

why would it scare them ? when amd added pcie 4 to x570, intel fans were saying so ? its no big deal, most devices cant use it yet any way. which was true, but now, not so much, going from a 970 pro to a 980 pro for my OS drive, i noticed a speed increase when i installed win10, and a little bit of an increase for other things. amd could just do the same, use pcie 5 for the cpu to chipset link, and leave everything else as 4, for check box parity. has amd even mentioned what " x670 " could have for pcie support yet ?