Intel Xeon to get Crystal Well: E3-1284L v3

by Ian Cutress on March 10, 2014 7:44 AM EST- Posted in

- CPUs

- Intel

- Xeon

- Iris

- Crystal Well

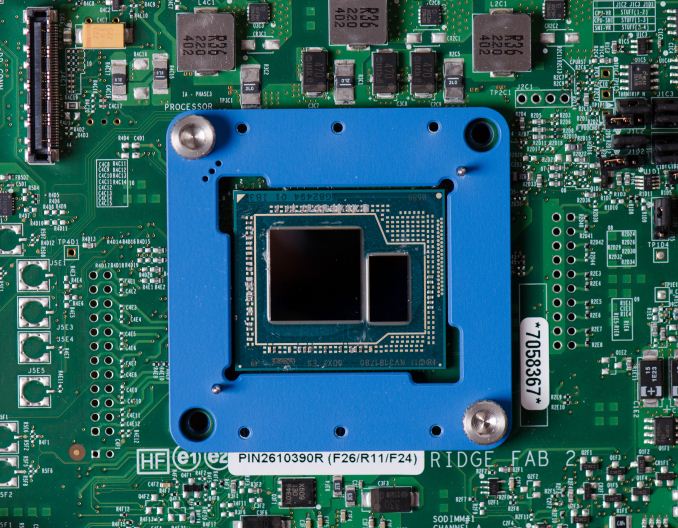

At both the Intel Haswell launch and the first shipping Haswell Xeon silicon, I lamented the lack of a Crystal Well Xeon part in the line-up. It would make sense that a large L4 cache on a CPU would be a prime target for workstation and server applications, as well as the gaming methodology used by Crystal Well in the Mac/Clevo laptops and Brix Pro system. Thus when searching for information on Xeon E3 SKUs today, my surprise came at the listing of Iris Pro 5200 enabled Xeon silicon.

Slipping somewhat under the radar, the Xeon E3-1284L v3 is a BGA only processor, featuring lower frequencies than any other Crystal Well SKU to date. The 47W quad-core part has a base clock of 1.8 GHz, hitting 3.2 GHz as the max turbo frequency. That is a big jump from base to turbo, so it would be interesting to see what the breakdown turbo frequencies are depending on per-core loading. As with the other similar SKUs, we have 32GB DDR3-1600 support, however ECC is supported and the memory bandwidth comparison on ark.intel.com would make this component aimed more for laptops and mobile devices rather than desktops. The integrated Iris Pro 5200 graphics have the highest base frequency of any Iris Pro part at 750 MHz, rising to 1.0 GHz at turbo which is incidentally the lowest turbo frequency of the Iris Pro 5200 range. vPro, VT-x, VT-d and TSX-NI are all enabled for this part as well.

Both CPU-World and ark.intel put the release of this part at Q1’14 (CPU-World states February 2014), however much like the initial Crystal Well parts, I would imagine we were 6 months out from seeing any products with the CPU coming to market. It could turn out that this SKU is just a specific customer’s request – it would seem a little odd just to have one processor of this nature in the Xeon line-up. But if your volume is sufficient, Intel might make it just for you.

Anand, Ganesh and I have each taken four separate looks at different Crystal Well hardware, including Intel’s Customer Reference Board, the iMac, a Clevo and the GIGABYTE Brix Pro.

35 Comments

View All Comments

ShieTar - Monday, March 10, 2014 - link

How much HPC is happening on Single-Socket Workstations, really?Torrijos - Monday, March 10, 2014 - link

This might be very useful when we see the new mac pro use case....You could render basic graphics with the integrated, while solely using the 2 big GPUs for openCL calculation, while right now one GPU is always bogged down by openGL screen management.

Adding-Color - Monday, March 10, 2014 - link

Freeing the big GPU from screen rendering work will be perfect.Hope this will be the case for most workstations in the not so distant future.

k2_8191 - Monday, March 10, 2014 - link

Oh, I thought Haswell variants of more than one socket Xeon have been released already, which is wrong.Yes, single-socket Xeons are not so suitable for HPC (I'm not sure whether lots of such Xeons densely integrated in racks will be OK though).

I hope they'll release Crystalwell version of E5-2687W v2...

Kevin G - Monday, March 10, 2014 - link

Haswell-E is rumored to also have eDRAM and a lot of it. With quad channel DDR4 support, Haswell-E is going to be a bandwidth monster.TiGr1982 - Monday, March 10, 2014 - link

I think, it won't happen. Haswell-E has NO GPU by definition, being just a renamed GPU-less Xeon E5 v3, so NO eDRAM as well, I suppose.DanNeely - Monday, March 10, 2014 - link

Crystalwell is connected over the same CPU IO hookup that is used for QPI in multi-processor links. In theory this means they could turn a 2P Xeon into a 1P + Cystalwell chip, or a 4P Xeon into a 2P model (replacing the ringbus connections with a single point to point link). I don't know if 8P models have more than 2 QPI ports, if they do they could be used to make 4P + crystalwell parts instead.Kevin G - Monday, March 10, 2014 - link

Where are you getting that they're using QPI for the eDRAM link? I was under the impression that it was something unique and proprietary.DanNeely - Monday, March 10, 2014 - link

I think I was mistaken. I went back to doublecheck an article from last month, but it was talking about Crystalwell and the on package southbridge in Haswell SoC models sharing at set of IO pins.http://www.anandtech.com/show/7744/intel-reveals-n...

TiGr1982 - Monday, March 10, 2014 - link

I mean, it's purely x86 CPU, so no eDRAM is requred for it in Intel's opinion.IMHO, for pure GPU-less x86-CPU, eDRAM may only happen for many-core Knights Landing later on:

http://www.realworldtech.com/knights-landing-detai...

but not for conventional multi-core Haswell-E.