DDR4 Haswell-E Scaling Review: 2133 to 3200 with G.Skill, Corsair, ADATA and Crucial

by Ian Cutress on February 5, 2015 10:10 AM EST

For any user interested in performance, memory speed is an important part of the equation when it comes to building your next system. This can apply to any user, from integrated graphics throughput to gaming and prosumer environments such as finance or oil and gas. Individuals with an opinion on memory speed fall into two broad camps, from saying faster memory has no effect, to the ‘make sure you get at least XYZ’. Following on from our previous Haswell DDR3 scaling coverage, we have now secured enough memory kits to perform a thorough test of the effect of memory speed on DDR4 and Haswell-E.

DDR4 vs. DDR3

On the face of it, direct comparisons between DDR4 and DDR3 are difficult to make. With the switch over from DDR2 to DDR3, there were some platforms that could use both types of memory and we could perform tests on both in the same environment. The current situation with DDR4 limits users to the extreme platform only, where DDR3 is not welcome (except for a few high minimum-order-quantity SKUs which are rarer than hens teeth). The platform dictates the memory compatibility, and the main characteristics of DDR4 are straightforward.

DDR4 brings to the table a lower operating voltage, down from 1.5 volts to 1.2 volts. This is the main characteristic touted by the memory manufacturers and those that use DDR4. It does not sound like a lot, especially when we can be dealing with systems from 300W to 1200W quite easily under Haswell-E. The quoted numbers are a 1-2W saving per module per system, which for a fully laden home-user desktop might approach 15W at the high end of savings over DDR3, but for a server farm with 1000 CPUs, this means a 15kW saving which adds up. The low voltage specification for DDR4L comes down from DDR3L as well, from 1.35 volts to 1.05 volts.

| DRAM Comparison | |||

| Low Voltage |

Standard Voltage |

Performance Voltage |

|

| DDR | 1.80 V | 2.50 V | |

| DDR2 | 1.80 V | 1.90 V | |

| DDR3 | 1.35 V | 1.50 V | 1.65 V |

| DDR4 | 1.05 V | 1.20 V | 1.35 V |

The lower voltage is also enhanced by voltage reference ICs before each memory chip in order to ensure that a consistent voltage is applied across each of them individually rather than the whole module at once. With DDR3, a single voltage source was applied across the whole module which can cause a more significant voltage drop, affecting stability. With this new design any voltage drop is IC dependent and can be corrected.

The other main adjustment to make from DDR3 to DDR4 is the rated speed. DDR3 JEDEC specifications started at 800 MTs and moved through to 1600 MTs, while some of the latest Intel DDR3 processors moved up to 1866 and AMD up to 2133. DDR4’s initial JEDEC for most consumer and server platforms is set at 2133 MHz, coupled with an increase in latency, but is designed to ensure that persistent transfers are quicker but overall latency is comparable to that of DDR2 and DDR3. Technically there is a DDR4-1600 specification for scenarios that want the bargain basement memory and are unfazed by actual performance.

As a result of this increase in speed, overall bandwidth is increased as well.

| Bandwidth Comparison | |||||

| Bus Clock | Internal Rate | Prefetch | Transfer Rate | Channel Bandwidth | |

| DDR | 100-200 MHz | 100-200 MHz | 2n | 0.20-0.40 GT/s | 1.60-3.20 GBps |

| DDR2 | 200-533 MHz | 100-266 MHz | 4n | 0.40-1.06 GT/s | 3.20-8.50 GBps |

| DDR3 | 400-1066 MHz | 100-266 MHz | 8n | 0.80-2.13 GT/s | 6.40-17.0 GBps |

| DDR4 | 1066-2133 MHz | 100-266 MHz | 8n | 2.13-4.26 GT/s | 12.80-25.60 GBps |

Latency moves from DDR3-1600 at CL 11 to DDR4-2133 at CL 15, which was an expected jump as JEDEC tends to increase CL by 2 for a jump in frequency. While having a latency of 15 clocks might come across as worse, the fact that the clocks are at 2133 MTs ensures that the overall performance is still comparable. At DDR3-1600 and CL11, time to initiate a read is 13.75 nanoseconds, compared to 14.06 nanoseconds for DDR4-2133 at CL15, which is a 2% jump.

One of the things that will offset the increase in latency is that CL15 seems to be a common standard no matter what frequency the memory is. Currently on the market we are seeing modules range from DDR4-2133 CL15 up to DDR4-3200 CL15 or DDR4-3400 CL16, marking a read latency down to 9.375 nanoseconds. With DDR3, we saw kits of DDR3-2400 CL10 for 8.33 nanoseconds, showing how aggressive memory manufacturing over the lifetime of the product can increase the efficiency.

Another noticeable difference from DDR3 to DDR4 is the design of the module itself.

DDR3 (top) vs DDR4 (bottom)

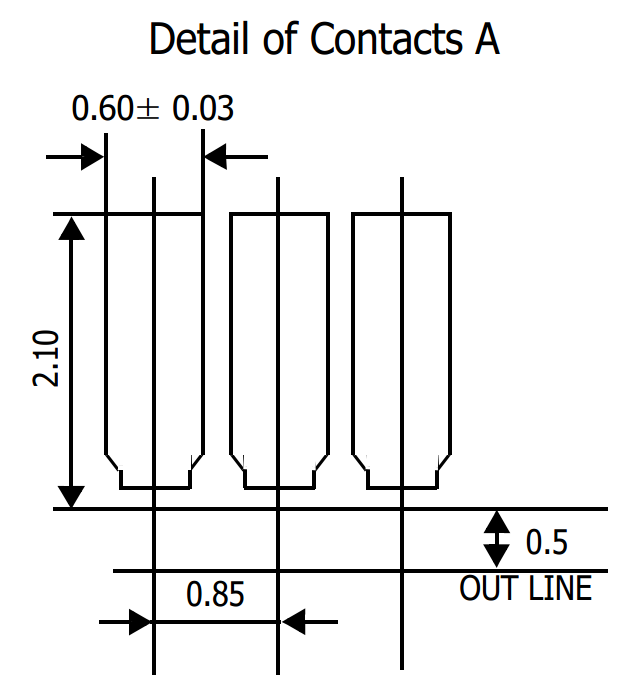

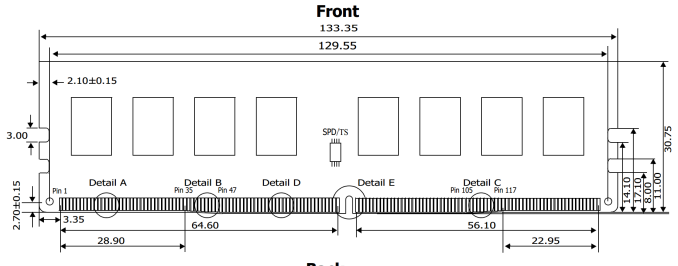

As with most technology updates notches are shifted in order to ensure that the right product fits in the right hole, but DDR4 changes a bit more than that. DDR4 is now a 288-pin package, moving up from 240-pin in DDR3. As the modules are the same length, this means a reduction in pin-to-pin distance from 1.00 mm to 0.85 mm (with a ±0.13 tolerance), decreasing the overall per-pin contact.

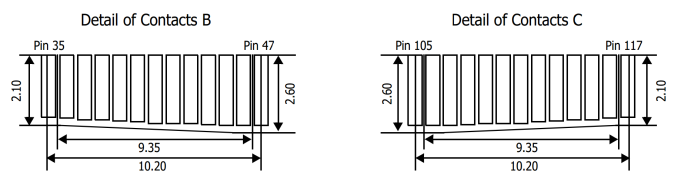

The other big design change is the sticky-out bits in the middle. Moving from pin 35 to pin 47, and back from pin 105 to pin 117, the pin contacts get longer as well as the PCB by 0.5 mm.

This is a gradient change rather than a full quick change:

Initially when dealing with these modules, I had the issue of not actually placing them in the slot correctly when using a motherboard with single sided latches. Over the past couple of weeks it has started to make more sense to place both ends in at the same time due to this protruding design, despite the fact it can be harder to do when on your hands and knees in a case.

Along with the pin size and arrangement, the modules are ever so slightly taller than DDR3 (31.25 mm rather than 30.35mm) to make routing easier, and the PCB is thicker (1.2 mm from 1.0 mm) to allow for more signal layers. This has implications for future designs, which we will mention later in the review.

There are other non-obvious benefits and considerations baked into the DDR4 design to mention.

DDR4 supports a low-power auto self-refresh (listed in the documentation as LPASR) which does the standard thing of refreshing the contents of memory but uses an adaptive algorithm based on temperature in order to avoid signal drift. The refreshing modes of each module will also adjust each array independently as the controller must support a fine-grained optimization routine to also coincide which parts of the memory are being used. This has power as well as stability implications for the long term future of DDR4 design.

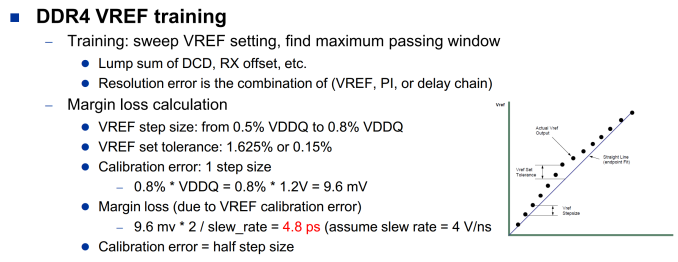

Module training when the system boots is also a key feature of DDR4. During the start-up routine, the system must sweep through reference voltages to find a maximum passing window for the speeds selected rather than just apply the voltage in the options. The training will go through the voltage reference in steps from 0.5% of the VDDQ (typically 1.2V) to 0.8% and the set tolerance of the module must be within 1.625%. Calibration errors are plausible at one step size (9.6 mV at 1.2V) but also the slew margin loss due to calibration error must also be considered. This is due to the greater implication of losses due to margins and tolerances and ensures stable operation during use. The downside to the user is that the number of modules in the system effects the boot time of the device. A fully laden quad-channel Haswell-E system adds another 5-8 seconds to perform this procedure, and it is something that cannot be circumvented through a different routine without disregarding part of the specifications.

Source: Altera

DDR4 is also designed with the future in mind. Current memory on the market, except what we saw with Intelligent Memory, is a monolithic die solution. The base JEDEC specification will allow for 3D stacking of dies with through-silicon-vias (TSVs) should any memory manufacturer wish to go down this route to increase module density. To support this adjustment there are 3 chip select signals, bringing the total of bank select bits to 7 for a total of 128 possible banks. At current UDIMM specifications, there is provision for up to 8 stacked dies, however DDR4 is listed only to support x4/x8/x16 ICs with capacities of 2, 4, 8 and 16 Gibit (gibibit). This would suggest that the stacked die configuration is more suited to devices where x-y dimensions are a premium, or in the server markets. When it comes to higher capacity modules, we have already reported that 16GB UDIMMs should be coming to market, representing an 8*16Gb dual rank arrangement. We are working to make sure we can report on these as soon as they land, however when it comes to higher density UDIMM parts (i.e. not RDIMM or LRDIMM) we might have to start looking at newer technologies.

There are a significant number of other differences between DDR4 and DDR3, but most of these lie in the electronic engineer/design role for the memory and motherboard manufacturers, such as signal termination, extra programmable latencies and internal register adjustment. For a more in-depth read into these, a good Google search can yield results, although a thorough understanding of Rajinder Gill’s AnandTech piece about ‘Everything You Always Wanted To Know About SDRAM But Were Afraid To Ask’ is a great place to start about general memory operation. I still go back and refer to that piece more frequently than I admit, and end up scratching my head until I reach bone.

120 Comments

View All Comments

dgingeri - Thursday, February 5, 2015 - link

Really, what applications use this bandwidth now?I'm the admin of a server software test lab, and we've been forced to move to the Xeon E5 v3 platform for some of our software, and it isn't seeing any enhancement from DDR4 either. These are machines and software using 256GB of memory at a time. The steps from Xeon E5 and DDR3 1066 to E5 v2 and DDR3 1333 and then up to the E5 v3 and DDR4 2133 are showing no value whatsoever. We have a couple aspects with data dedup and throughput are processor intensive, and require a lot of memory, but the memory bandwidth doesn't show any enhancement. However, since Dell is EOLing their R720, under Intel's recommendation, we're stuck moving up to the new platform. So, it's driving up our costs with no increase in performance.

I would think that if anything would use memory bandwidth, it would be data dedup or storage software. What other apps would see any help from this?

Mr Perfect - Thursday, February 5, 2015 - link

Have you seen the reported reduction in power consumption? With 256GBs per machine, it sounds like you should be benefiting from the lower power draw(and lower cooling costs) of DDR4.Murloc - Thursday, February 5, 2015 - link

depending on the country and its energy prices, the expense to upgrade and the efficiency gains made, you may not even be able to recoup the costs, ever.From a green point of view it may be even worse due to embodied energy going to waste depending on what happens to the old server.

Mr Perfect - Friday, February 6, 2015 - link

True, but if you have to buy DDR4 machines because the DDR3 ones are out of production(like the OP), then dropping power and cooling would be a neat side bonus.And now, just because I'm curios: If the max DDR4 DIMM is 8GB, and there's 256GB per server, then that's 32 DIMMs. 32 times 1 to 2 watts less a DIMM would be 32 to 64 watts less load on the PSU. If the PSU is 80% efficient, then that should be 38.4 to 76.8 watts less at the wall per machine. Not really spectacular, but then you've also got cooling. If the AC is 80% efficient, that would be 46.08 to 92.16 watts less power to the AC. So in total, the new DDR4 server would cost you (wall draw plus AC draw) 84.48 to 168.96 watts lower load per server versus the discontinued DDR3 ones. Not very exciting if you've only got a couple of them, but I could see large server farms benefiting.

Anyone know how to work out the KWh and resulting price from electric rates?

menting - Friday, February 6, 2015 - link

100W for an hour straight = 0.1KWH. If you figure 10-20 cents per KWH, it's about 1-2 cents per hour for a 100W difference. That's comes to about $7-$14 per month in bills provided that 100W is consistent 24/7.menting - Thursday, February 5, 2015 - link

pattern recognition is one that comes to mind.Murloc - Thursday, February 5, 2015 - link

physical restraints of light speed? Isn't any minuscule parasitic capacitance way more speed limiting than that?menting - Thursday, February 5, 2015 - link

there's tons of limiting factors, with capacitance being one of those. But even if you take pains to optimize those, the one factor that nobody can get around is the speed of light.menting - Thursday, February 5, 2015 - link

i guess i should say speed of electricity in a conductive medium instead of speed of light.retrospooty - Friday, February 6, 2015 - link

Agreed if an app required high total bandwidth it would benefit.Now see if you can name a few that actually need that.