Imagination Announces New P6600, M6200, M6250 Warrior CPUs

by Andrei Frumusanu on November 10, 2015 3:15 AM EST

Today Imagination launches three new MIPS processor IPs: One in the performance category of Warrior CPUs, the P6600 and two embedded M-class core, the M6200 and M6250.

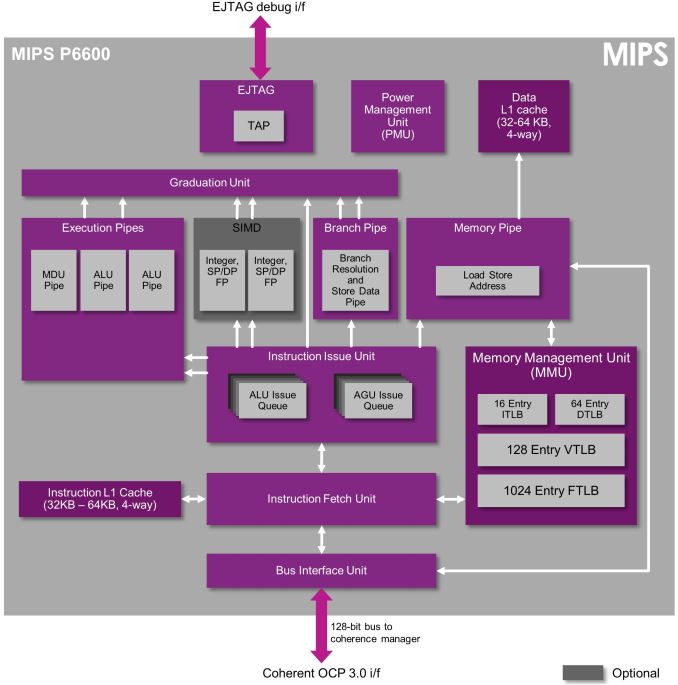

Warrior P6600

Starting off with the P6600, this is Imagination's new MIPS flagship core succeeding the P5600. The P5600 was a 3-wide out-of-order design with a pipeline depth of up to 16 stages. The P6600 keeps most of the predecessor's characteristics such as the main architectural features or full hardware virtualization and security through OmniShield, but adds compatibility for MIPS64 64-bit processing on top. Imagination first introduced a mobile oritented 64-bit MIPS CPU back with the I6400 a little more than a year ago but we've yet to see vendors announce products with it.

We're still lacking any details on the architectural improvements of the P6600 over the P5600 so it seems that for now we're left with guessing what kind of performance the new core will bring. The P5600 was directly competing with ARM's Cortex A15 in terms of IPC, but ARM has since then not only announced but also seen silicon with two successor IPs to the A15 (A57 and A72), so the P6600 will have some tough competition ahead of itself once it arrives in products.

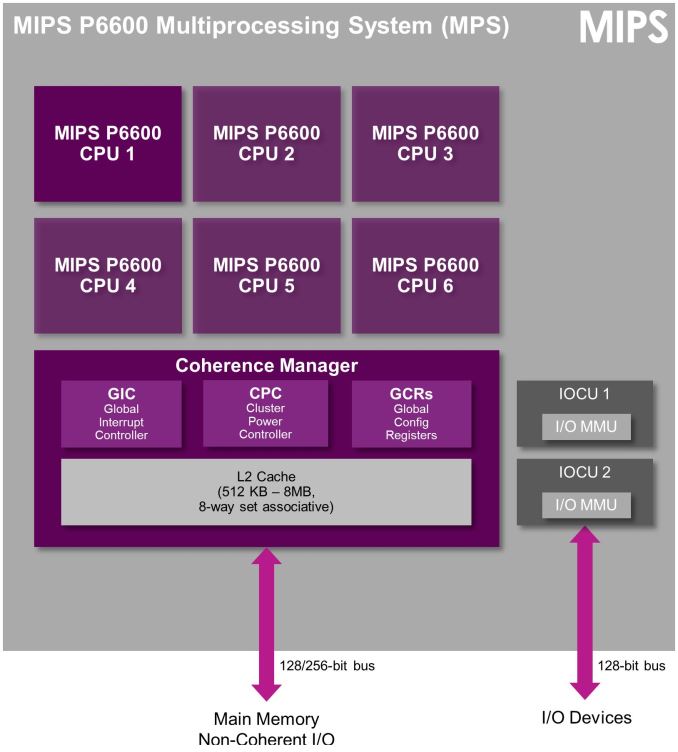

The P6600, much like the P5600 can be implemented from single-core to six-core cluster configurations. What is interesting that as opposed to ARM CPU IP, the MIPS cores allow for asynchronous clock planes between the individual cores if the vendors wishes to implement the SoC's power management in this way (It can also be set up to work in a synchronous way).

"MIPS P6600 is the next evolution of the high-end MIPS P-class family and builds on the 32-bit P5600 CPU. P6600 is a balanced CPU for mainstream/high-performance computing, enabling powerful multicore 64-bit SoCs with optimal area efficiency for applications in segments including mobile, home entertainment, networking, automotive, HPC or servers, and more. Customers have already licensed the P6600 for applications including high-performance computing and advanced image and vision systems."

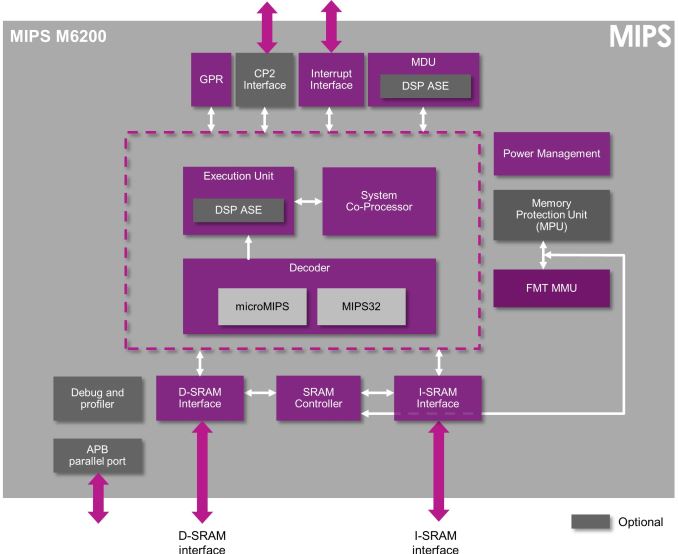

Warrior M6200 & M6250

Also as part of today's announcement we see two new embedded CPU cores, the M6200 and M6250. Both cores are successors to the microAptiv-UP and UC but able to run at up to 30% higher frequency. The new processors also see an ISA upgrade to MIPS32 Release 6 instead of Release 5.

The M6200 is targeted at real-time embedded operating systems with minimal funtionality for cost- and power-savings. It has no MMU and as such can only be described as a microcontroller part.

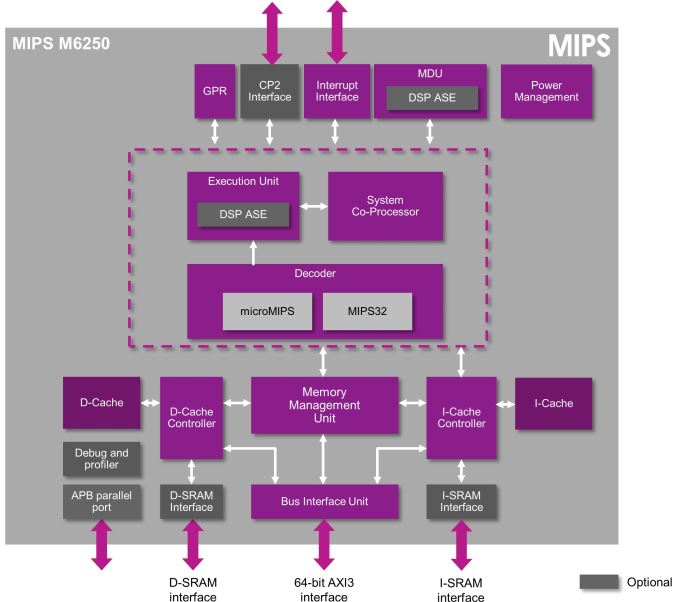

The M6250 is the bigger brother of the M6200 and the biggest difference is the inclusion of a memory management unit (MMU) that makes this a full fledged processor core that can run operating systems like Linux.

"M6200 and M6250 are configurable and fully synthesizable solutions for devices requiring a high level of performance efficiency and small silicon area including wireless or wired modems, GPU supervisors, flash and SSD controllers, industrial and motor control, advanced audio and more."

15 Comments

View All Comments

ruthan - Tuesday, November 10, 2015 - link

Any info about TDP?SarahKerrigan - Tuesday, November 10, 2015 - link

"The P6600 keeps most of the predecessor's characteristics such as hardware multi-threading of up to 4 threads per core"P5600 wasn't multithreaded. The previous multithreaded Imgtec cores were interAptiv and I6400 (and, if I recall, 34Kc before that.)

SarahKerrigan - Tuesday, November 10, 2015 - link

Actually, I'm not seeing any other source, including Imgtec, saying P6600 is multithreaded either. I suspect Anandtech may be misreporting here.Andrei Frumusanu - Tuesday, November 10, 2015 - link

You're right, I mixed up the I6400's multi-threading with the P5600's capabilities.Arnulf - Wednesday, November 11, 2015 - link

Hello Alex Voica, I have slightly off-topic question for you if I may:Can we expect CI20 upgrade with faster CPU anytime soon, perhaps some of this P6600 stuff trickling into JZ line?