Nantero Exits Stealth: Using Carbon Nanotubes for Non-Volatile Memory with DRAM Performance & Unlimited Endurance

by Kristian Vättö on June 11, 2015 12:35 PM EST- Posted in

- Storage

- DRAM

- Semiconductors

- Nantero

- NRAM

The race for next generation non-volatile memory technology is already on at full throttle. We covered Crossbar’s ReRAM announcement last year and last week a very exciting company with a different non-volatile technology exited stealth mode and shed light on its technology and commercialization plans. The company is called Nantero and it’s been developing its NRAM technology for well over a decade now.

Before we talk about the technology itself, let’s briefly discuss the company and its key persons as Nantero is probably an unfamiliar name to many (it was for me, at least). The company was founded by Greg Schmergel, Dr. Tom Rueckes and Dr. Brent M. Segal in 2001. Mr. Schmergel and Dr. Rueckes are both still with the company and serve as CEO and CTO respectively, but Dr. Segal left the company in 2008 as a part of Nantero's Government Business Unit acquisition by Lockheed Martin. Mr. Schmergel is a well renowned serial entrepreneur who founded ExpertCentral that was later acquired by About.com where Mr. Schmergel served as a Senior Vice President before co-founding Nantero. While Mr. Schmergel brings valuable business expertise to the company, the technology comes from Dr. Tom Rueckes who is a Harvard Ph.D in chemistry and the inventor of NRAM technology.

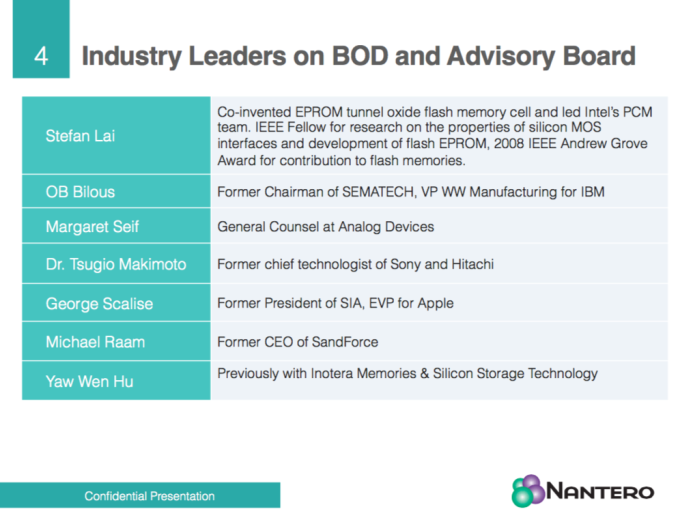

The Board of Directors includes several semiconductor industry veterans. Mr. Lai was one of the leading developers of NAND technology at Intel and also led Intel’s Phase Change Memory (PCM) team. Dr. Makimoto is a former Chief Technologist of Sony and Hitachi and Mr. Scalise is actually the former President of Silicon Industry Association (SIA) and also served as an Executive Vice President at Apple briefly in the late 90s. Mr. Raam may too be a familiar name to some since he is the former CEO of SandForce (the SSD controller company) that is now owned by Seagate.

The Technology

It goes without saying that Nantero is packed with semiconductor experience and know-how, but its technology isn’t any less interesting. NRAM is made out of carbon nanotubes, which is the strongest material known to man and provides far better thermal and electrical conductivity than any other known material.

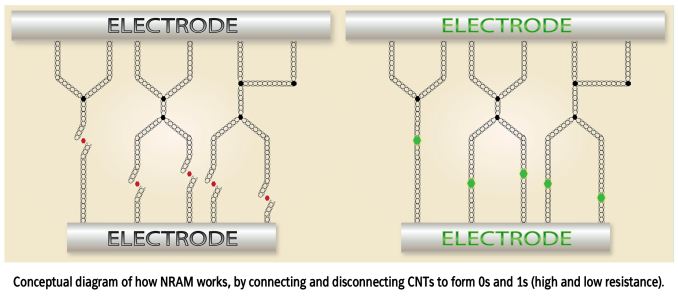

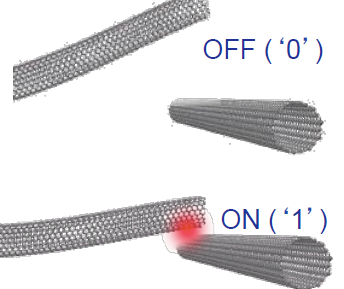

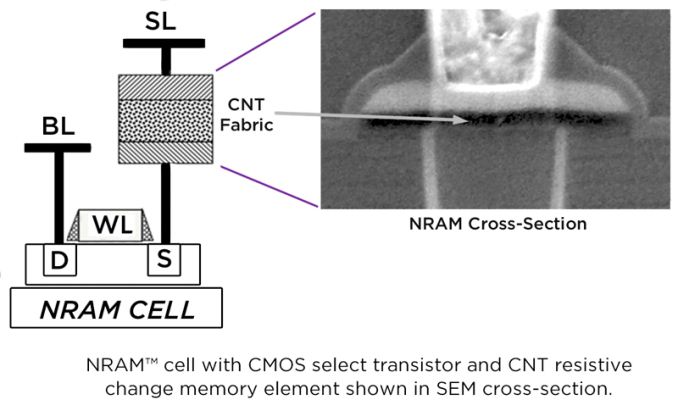

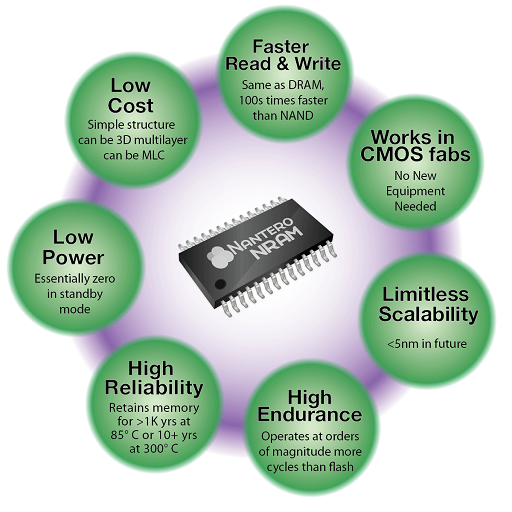

The way NRAM works is in fact relatively simple. Essentially there are two nanotubes, which have low resistance when in physical contact and high resistance when separated. The amount of resistance then determines whether the cell is considered to be programmed as ‘0’ or ‘1’. Program operation (or “SET” as Nantero calls it) works by applying a voltage on one of the nanotubes, which will then attract the other nanotube and create a bond. The SET operation is very fast and takes only picoseconds, which is on par with or better than DRAM latency. The bond is kept in tact by Van der Waal's interactions and is practically immortal with data retention terms even in 300°C is over ten years. In an erase operation (or RESET as Nantero calls it) the voltage is simply applied in the other direction, which will “heat up” (given the scale it’s more like vibration) the nanotube contacts and cause them to separate. Given that carbon nanotubes are one of the strongest materials in the world, the write/erase endurance is practically infinite as independent university study has shown Nantero’s NRAM technology to have over 1011 P/E cycles (for your information, 1011 translates to 100 billion).

The other great news is that carbon nanotubes are extremely small. One nanotube can have a diameter of only 2nm and the pitch between the two nanotubes in off-state can be an even tinier 1nm, so the technology has potential to scale below 5nm. NRAM can also scale vertically, or go 3D, and since the cell structure and manufacturing process are both quite simple, 3D stacking should, in theory, be much easier compared to what 3D NAND is today with no need for high aspect ratio etching as an example.

The Manufacturing Process

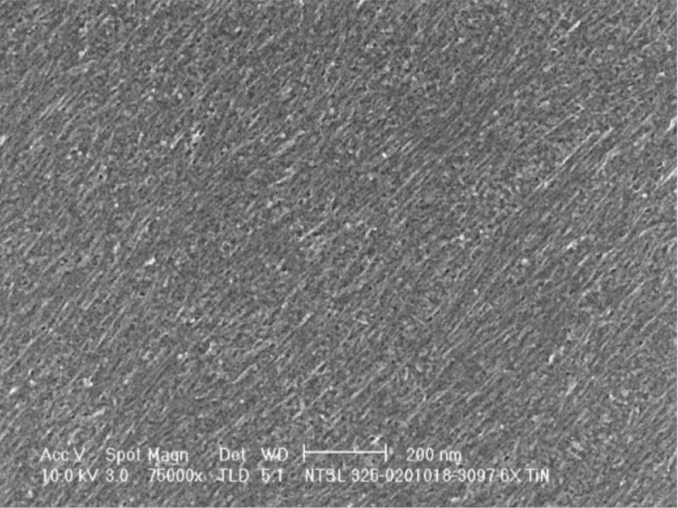

The process of making an NRAM wafer starts by taking a normal CMOS wafer with the normal cell select and array line circuitry, which is then spin coated with carbon nanotubes. Carbon nanotubes are grown from iron that would normally contaminate a clean room, thus Nantero had to develop a patented process that creates ‘pure’ carbon nanotubes with less than one out of billion particles being foreign (the standard for the highest quality clean rooms). Nantero has worked hard in the past two years to bring the cost of carbon nanotubes down and currently the company says that the nanotubes have a negligible impact on chip cost, meaning making NRAM isn't inherently more expensive than any other semiconductor.

Top-down SEM of NRAM

With the nanotubes on the wafer, the top electrode is deposited on top of the nanotubes, followed by the photoresist, which is then patterned using a single mask. Finally the wafer is etched to cut the nanotubes into smaller pieces (i.e. more memory cells) and that’s it in a nutshell. Obviously there are other general semiconductor processing steps involved, but those are the same for all memory technologies, so the fundamental process of manufacturing NRAM isn’t that complex. All that is needed is a normal CMOS fab because the NRAM process requires no special or additional tools.

Fortunately, NRAM isn’t just a technology that exists on paper. Nantero’s NRAM process has already been installed in seven production CMOS fabs ranging from 20nm to 250nm and limited production has been taking place for several years now, although only in small few megabit capacities. As a matter of fact, Nantero completed a successful space test with NASA on Space Shuttle Atlantis back in 2009 where NRAM operated without any shielding throughout the trip without any errors despite the intense radiation, because as I mentioned earlier, the nanotube bonds are practically unbreakable and are not affected by heat, magnetism, radiation and the like.

Nantero’s Business Plan: Bringing NRAM to Everyone

Because Nantero is an IP licensing company, it relies solely on its partners for production. It's a logical strategy because a decent sized fab requires an investment in the order of billions of dollars and in the end the company would have to compete against Intel, Samsung and the rest of the semiconductor giants. Actual end products will be sold under the manufacturer's brand (e.g. Intel), so you won't see any Nantero branded products on the market.

Nantero isn't disclosing any of its partners at this point as most of them are still developing products that have the potential for higher volume production. While Nantero has its own chip team that is developing high capacity (several gigabits) dies, every partner is also doing its own work to implement NRAM at a larger scale, which makes sense given that the big semiconductor companies have far more resources and are familiar with high capacity memory devices.

Aside from semiconductor companies, Nantero has also partnered with several more consumer-facing companies to develop concepts and products around NRAM technology. Since NRAM provides the same level of performance as DRAM but is non-volatile, NRAM could open the doors for products that aren't achievable (at least properly) with today's NAND and DRAM technology. As examples Nantero mentions 3D smartphones and commercial 3D printers (although to be frank both already exist to some extent), but practically anything that's handicapped by IO performance and volatility can be fixed with NRAM in the future.

Since it will take several years before NRAM is even close to modern NAND capacities, Nantero has a three step strategy of bringing NRAM to the market. In the first step Nantero is simply offering a class of memory (both standalone and embedded) that has DRAM's performance characteristics and NAND's non-volatility. Technically that means NRAM is competing against current MRAM and ReRAM products for a specialized niche market that really needs high performance and non-volatility. The consumer market is obviously not one of those and even for the enterprise NRAM is likely too small capacity and expensive, but the industrial and especially space/military applications should benefit from NRAM despite the high initial cost.

The next step is to grow NRAM to gigabit-class capacities and offer a non-volatile alternative to DRAM. Going to gigabit-class certainly opens the doors for NRAM as a mainstream memory because it could be used for a variety of caching applications that benefit from non-volatility (SSDs with their DRAM caches for NAND mapping table are a prime example). Tape out of first gigabit NRAM wafers is still about 18 months away, so I would expect to see something shipping perhaps in late 2017 or 2018.

The final step, of course, is a terabit-class die to replace NAND (FYI, Samsung is projecting 1Tbit NAND die in 2017). Achieving that requires work on both lithography scaling and 3D integration technologies because such a high capacity die is only economical with either multiple layers or advanced lithography, or both.

NRAM also has the potential to operate in MLC mode for further density improvements, but for now Nantero is focusing on scaling NRAM down and adding layers through 3D to increase density. Once the work on those two is done and has been implemented to a production fab, Nantero will start commercializing NRAM MLC technology, but that is likely at least several years away.

Final Words

The announcement is intriguing to say the least. From a technology standpoint NRAM sounds very exciting because it's effectively bringing us non-volatile DRAM performance, and better yet the cell design is scalable whereas DRAM has major struggles going below 20nm. I like the fact that Nantero has decided to go with IP licensing model because it means that NRAM is a technology available to everyone. The reason why DRAM and NAND are where they are today is because there are multiple companies producing them, resulting in competition with billions of R&D dollars.

I wonder if any of the big semiconductor companies has partnered with Nantero yet. Most of them have been tight-lipped about their post-NAND plans, but maybe Nantero's announcement will sooner than later force the companies to talk about their strategies. Obviously a lot depends on how far 3D NAND can efficiently scale, but from what I have heard the transition to next generation memory technologies should begin around 2020. The future of memory isn't here yet, but it's certainly getting closer and it will be interesting to see what technology ends up taking the crown.

35 Comments

View All Comments

nandnandnand - Thursday, June 11, 2015 - link

It wasn't it stealth mode. It was in fail mode:http://spectrum.ieee.org/semiconductors/memory/los...

http://spectrum.ieee.org/nanoclast/semiconductors/...

Shadow7037932 - Thursday, June 11, 2015 - link

This is pretty neat. But for DRAM replacement applications, wouldn't you need more than 100 billion PE cycles? FRAM in comparison has > 100 Trillion PE cycles.freeskier93 - Thursday, June 11, 2015 - link

The independent study said "over" 100 billion cycles, didn't say either what the results where after said 100 billion cycles. Could be they just stopped or they are still testing. Nantero is claiming near infinite cycles.ianmills - Thursday, June 11, 2015 - link

The slide says "orders of magnitude greater endurance than flash"Seems pretty incongruous to near infinite... sounds like a bunch of marketing fud!

mkozakewich - Thursday, June 11, 2015 - link

FUD is Fear, Uncertainty, and Doubt. This is the opposite of FUD.close - Friday, June 12, 2015 - link

A mathematician and a physicist agree to a psychological experiment. The mathematician is put in a chair in a large empty room and a beautiful naked woman is placed on a bed at the other end of the room. The psychologist explains, "You are to remain in your chair. Every five minutes, I will move your chair to a position halfway between its current location and the woman on the bed." The mathematician looks at the psychologist in disgust. "What? I'm not going to go through this. You know I'll never reach the bed!" And he gets up and storms out. The psychologist makes a note on his clipboard and ushers the physicist in. He explains the situation, and the physicist's eyes light up and he starts drooling. The psychologist is a bit confused. "Don't you realize that you'll never reach her?" The physicist smiles and replied, "Of course! But I'll get close enough for all practical purposes!"100 billion in this particular field can be considered infinite for all practical purposes. Also the theoretical physics behind the phenomenon says the carbon nanotubes should stand basically an infinite number of cycles.

tuxRoller - Friday, June 12, 2015 - link

I've never dealt with physicists who throw around the word "infinite" in the manner described.ToTTenTranz - Thursday, June 11, 2015 - link

My thoughts exactly.If the on/off cycle takes 2*20ns, then it'll be able to do 25 million cycles per second.

With that speed, constantly switching the same cell would reach those 100 billion cycles within 4000 seconds. That's 1 hour and 7 minutes. Of course the controller would be made so that the cells are used in the least repetitive way, but it's still not a very encouraging number.

I understand this can be successfully used as a replacement for flash storage, but it doesn't seem like this could be used as an unified solution for volatile and non-volatile memory.

azazel1024 - Friday, June 12, 2015 - link

But what is a typical RAM write leveling per day? 100GB? 1TB? 10TB?8GB of this stuff, with even 8TB of NRAM writes per day works out to about 300,000 years.

If there were even 8000TB of NRAM writes per day to 8GB of memory, that works out to 300 years.

I am sure in a typical day of use for most computers there are at least dozens of terabytes of writes to that RAM, but multiple petabytes (dozens)? That is what would be needed to push 100 billion P/E cycles in to the range of "only a few years of endurance".

A current typical processor and memory controller is looking at only around 20GB of writes per second to main memory. 8GB/20GB per second is .4s per full write. .4s x 100 billion is a LONG time. About 2,500 years.

You are not doing a full memory write/erase/re-write at the maximum speed of all of the cells constantly (I don't know of any controller that is capable of writing/erasing all cells at once in RAM, NAND, etc.).

hazydave - Sunday, June 14, 2015 - link

Write levelling isn't used in DRAM controllers. That's a relatively easy thing to implement for a storage controller in software. It would be more complicated to build in pure hardware for a DRAM replacement.